IWILDT-X光安檢機FPGA圖像數據排序算法實現

作者: / / 閱讀人數:0

在傳統的集裝箱安檢機數據采集傳輸係統中。控製芯片直接將ad采集的前端x射線探測器的數據傳輸到上位機中,然後上位機軟件在對數據進行排序整理然後在進行圖像數據的處理,這樣不僅降低了上位機CPU增加了處理負擔,而且降低了圖像數據的處理速度,大大降低了集裝箱安檢機的安檢效率;由武漢艾崴IWILDT -AN 10080設計利用FPGA的高速數據處理特性,通過對AD采集的前端雙能x射線探測器的圖像數據在雙端口RAM中進行排序處理,然後通過以太網將排序好的圖像數據傳輸到上位機中,這樣不僅降低了上位機的cpu的占用率提高了上位機圖像處理的速度,使集裝箱安檢機的實時性能得到更好的提高。

1 FPGA及雙端口RAM介紹

1.1 FPGA 簡介

FPGA的高速數據處理特性”,通過對AD采集的前FPGA是-種可編程芯片,主要應用與專用集成端雙能X射線探測器的圖像數據在雙端口RAM中.電路的設計,FPGA內部邏輯資源豐富,可以使用硬進行排序處理,然後通過以太網將排序好的圖像數件描述語言(Verilog或VHDL)根據需求對電路進行設計,然後通過編譯綜合,引腳分配後,通過JTAG或 AS將程序燒錄至FPGA中實現功能電路。並且用這些簡單的邏輯電路經過硬件編程後可以組成複雜的邏輯實現更高級的功能。FPGA具有抗幹擾能力強,運行速度快,可進行多次擦出的優點[4]。

1.2雙端口RAM

雙端口RAM是在1個SRAM存儲器上具有兩套完全獨立的數據線,地址線和讀寫控製線,並允許兩個獨立的係統同時對其進行隨機性訪問的存儲器,即共享式多端口存儲器。雙端口RAM最大的特點是存儲數據共享。用FPGA來實現雙端口RAM的功能可以很好地解決並行性和速度問題,而且其靈活的可配置特性使得基於FPGA的雙端口RAM易於進行修改、測試及係統升級,可降低設計成本,縮短開發周期[5]。

2集裝箱安檢機數據采集傳輸概述

目前大多數集裝箱安檢機數據采集傳輸流程大概都分為三步,首先通過由多個探測板組成的雙能x射線探測器對穿透物體後的x射線能量進行采集,然後每個探測板在接收到x射線能量後會根據能量的衰減增益輸出相應的像素值,像素值會以模擬電壓值的形式輸出到下一級,然後這些代表圖像像素信息的模擬電壓值通過模數轉換芯片將模擬電壓值轉換成圖像數字量送人到控製芯片,最後控製芯片將圖像數據通過網口或其他通信方式將圖像數據傳輸到上位機中,通過圖像處理軟件將圖像數據處理形成圖像以供安全檢查使用[61。

3整體設計框架

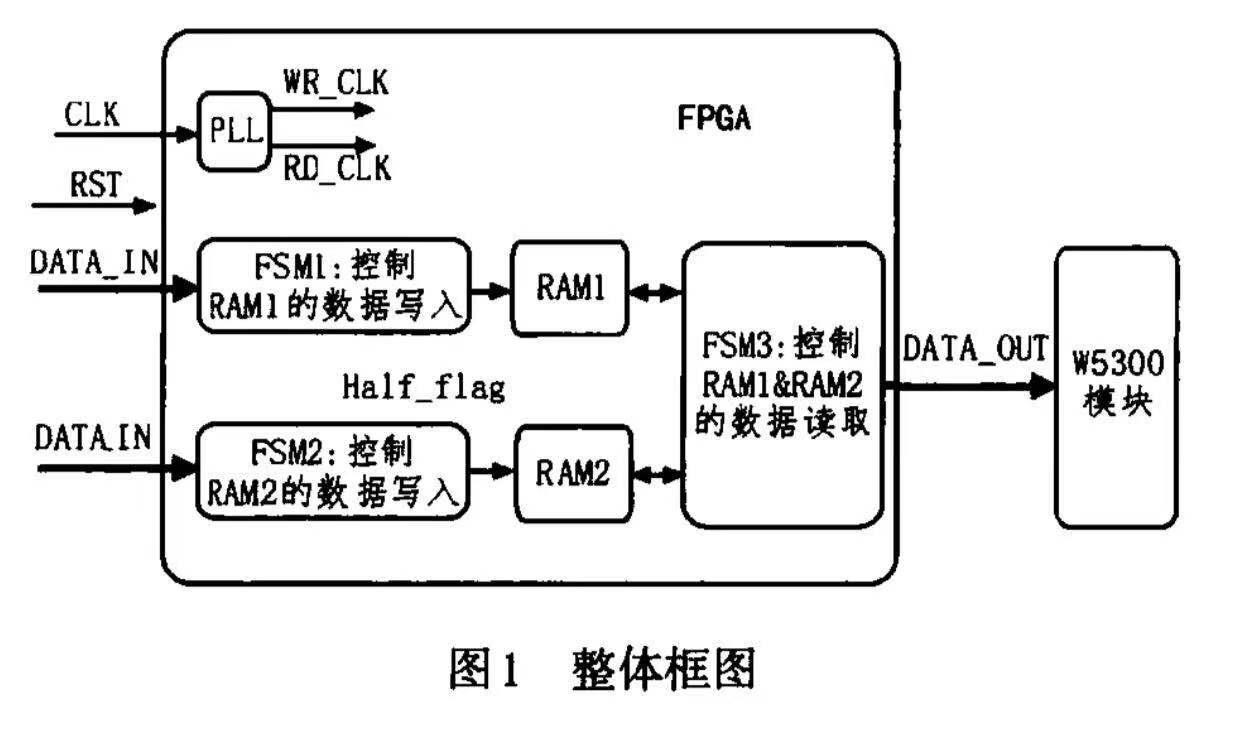

本設計主要利用FPGA中的雙端口RAM核對兩路AD采集到的圖像數據進行數據排序然後傳輸到上位機。前端采用兩個雙能x射線探測器采集圖像數據,每個探測器上最多可以連接8塊探測板,每個探測板會輸出128個像素值,其中包括先輸出的64 個低能像素值和後輸出的64個高能像素值。兩路 AD分別對這兩個雙能x射線探測器所輸出的高低能像素值進行模數軟換為16位位寬的圖像數據並送至FPCA,然後FPCA通過控製使圖像數據能夠按一定順序存儲在雙端口RAM中以供後續通過網口或其他通信方式傳輸到上位機進行圖像數據處理。由於本實現方法都在FPGA中實現,所以在 FPCA中主要通過兩個雙端口RAM以及RAM控製模塊來實現圖像數據的排序。首先對於前端兩路數據輸人分別通過兩個RAM控製模塊緩存到兩個 RAM中並排序,然後通過一個讀取RAM控製模塊將兩個RAM中的緩存數據讀出,整體框圖如圖1所示。

3· 1雙端口皿M核設計

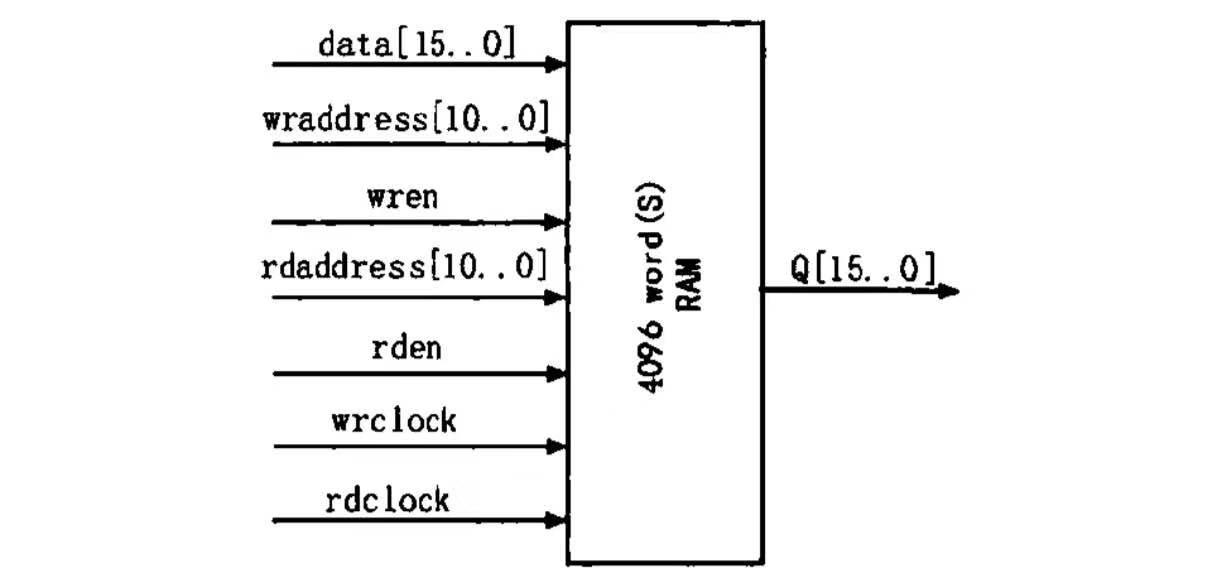

針對本集裝箱安檢機數據采集傳輸係統,將在FPGA 內部例化兩個雙端口RAM核,如此可以將兩路AD 所采集的圖像數據分別緩存到RAM中進行排序。由於AD所轉換的是16位位寬數據,所以RAM的數據輸人和輸出端均為16位位寬,每一個AD所接前端探測器的探測板最多為8個,所以一次采集的圖像數據大小最大為1 024個16位數據,為了在讀取 RAM數據的同時前端圖像數據還可以繼續存人 RAM中,所以設置RAM核的深度為2048,地址總線寬度設置為11位位寬,由於設計中數據讀出時鍾是寫人時鍾的5倍,所以讀時鍾和寫時鍾均由PLL鎖相環倍頻得到。由於兩路AD所采集的圖像數據性質是一樣的,所以在FPGA中例化的這兩個雙端口 RAM核所包含的引腳均一樣,雙端口RAM模塊示意圖如圖2所示。

圖2雙端口RAM模塊

引腳說明:data[ 15..0]為16位位寬數據輸人端口;wraddress[10..0]為11位位寬寫數據地址端口; wren為RAM寫使能端口,高有效;rdaddress[10..0]為11位位寬讀數據地址端口;rden為RAM讀使能端口,高有效;wrclock為RAM寫數據時鍾端口; rdclock為RAM讀數據時鍾信號;q[15..0]為16位位寬數據輸出信號。

3·2數據寫入RAM控製模塊

由於前端探測器所采集的數據的類型與排序方式是一樣的,所以在這裏隻針對一路數據寫人RAM 的控製模塊進行闡述。首先根據前端x射線探測器所接探測板的數量的不同,AD持續采集數據的時間也會不同,例如ADI前端探測器接了3塊探測板, AD2前端探測器接了4塊探測板,那麽兩路AD同時開始采集圖像數據,並且ADI在采集了3塊探測板的圖像數據之後要等待AD2采集完4塊探測板之後再開始采集下一次的數據。

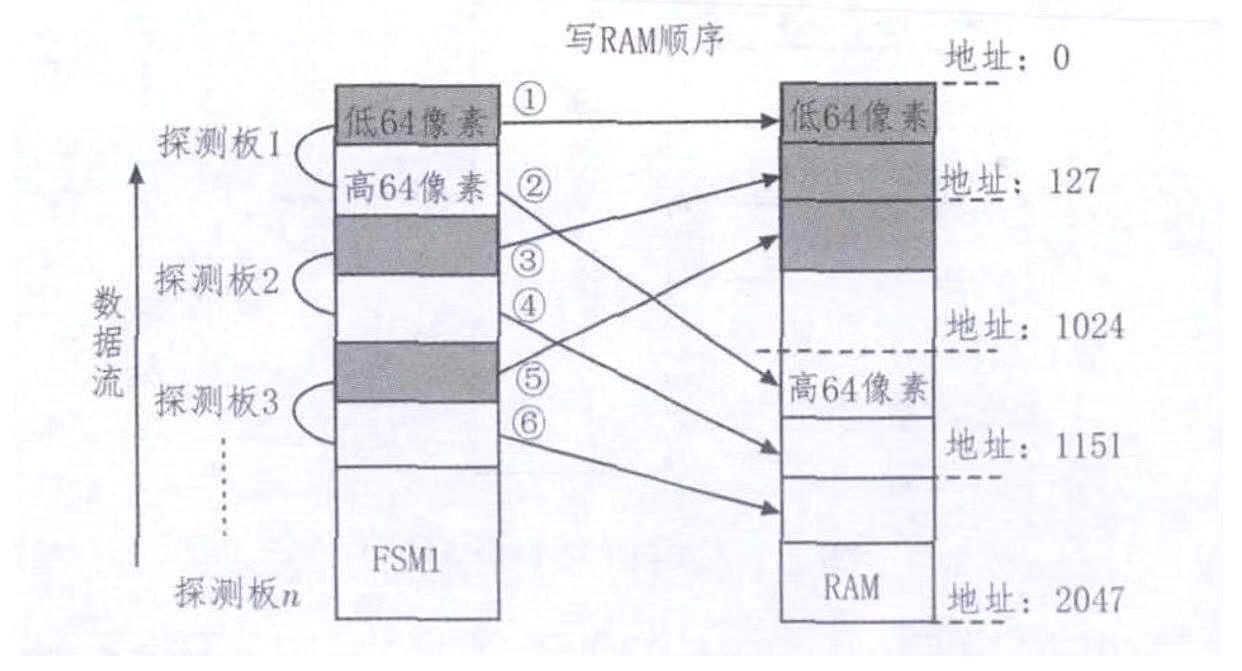

前端雙能x射線探測器的每個探測板會輸出 128個像素值,其中包含64個低能像素值和64個高能像素值,而最終要分別組成高低能兩幅圖像則首先要把每路的高低能像素值分段存儲在RAM中。由於前端探測器所輸出的順序先是探測板1的64個低能像素值然後64個高能像素值,再然後是探測板 2的64個低能像素值然後64個高能像素值,所以數據寫人RAM的控製模塊中首先要將高低能像素值分別緩存到RAM的不同區域中以供後續取出。

當前端探測器數據開始采集之後,本模塊首先將依次到來的探測板1的64個低能像素值依次存人到雙端口RAM 1的0到63地址,隨後將探測板1的 64個高能像素值依次緩存到雙端口RAMI的1024 到1087地址;然後再將探測板2的64個低能像素值存人到RAMI的64到127地址,隨後將探測板2的 64個高能像素值緩存到RAMI的1088到1巧1地址,並遵循此緩存規律將AD采集的高低能圖像數據緩存到RAMI中,如圖3所示。

3寫RAM示意圖

在將前端x射線探測器數據寫人RAM的期間,因為前端接人探測板的數目不同,所以會導致其中一路優先全部寫人RAM中,因此本設計編程思路是如果其中一個RAM將前端采集到的數據全部寫人之後變監測另一路數據是否也全部寫人RAM中,如果沒有則等待,如果兩路都已經緩存完畢則開始下一次的數據采集和緩存。並且數據寫人RAM的地址會根據當前地址進行規律遞增,當低能圖像數據緩存到1 023地址後,下一低能圖像數據將會0地址開始緩存,而高能圖像數據緩存到2047地址後,下一個高能圖像數據將會從1 024地址開始緩存。

3·3數據讀出RAM控製模塊

RAM讀取的速率一般都比寫人RAM的速率快,所以本設計用5倍於寫人速率的讀時鍾來進行數據的讀取。因此必須注意時鍾追趕的問題,及讀出一定要滯後寫人,否則讀出的數據就不是存人雙端口 RAM的數據。因此本設計編程思想是在緩存一次前端探測器采集的數據之後發出可讀數據標誌位,然後數據讀出RAM控製模塊將這一次緩存的圖像數據讀出來,然後等待下一次的可讀標誌位。

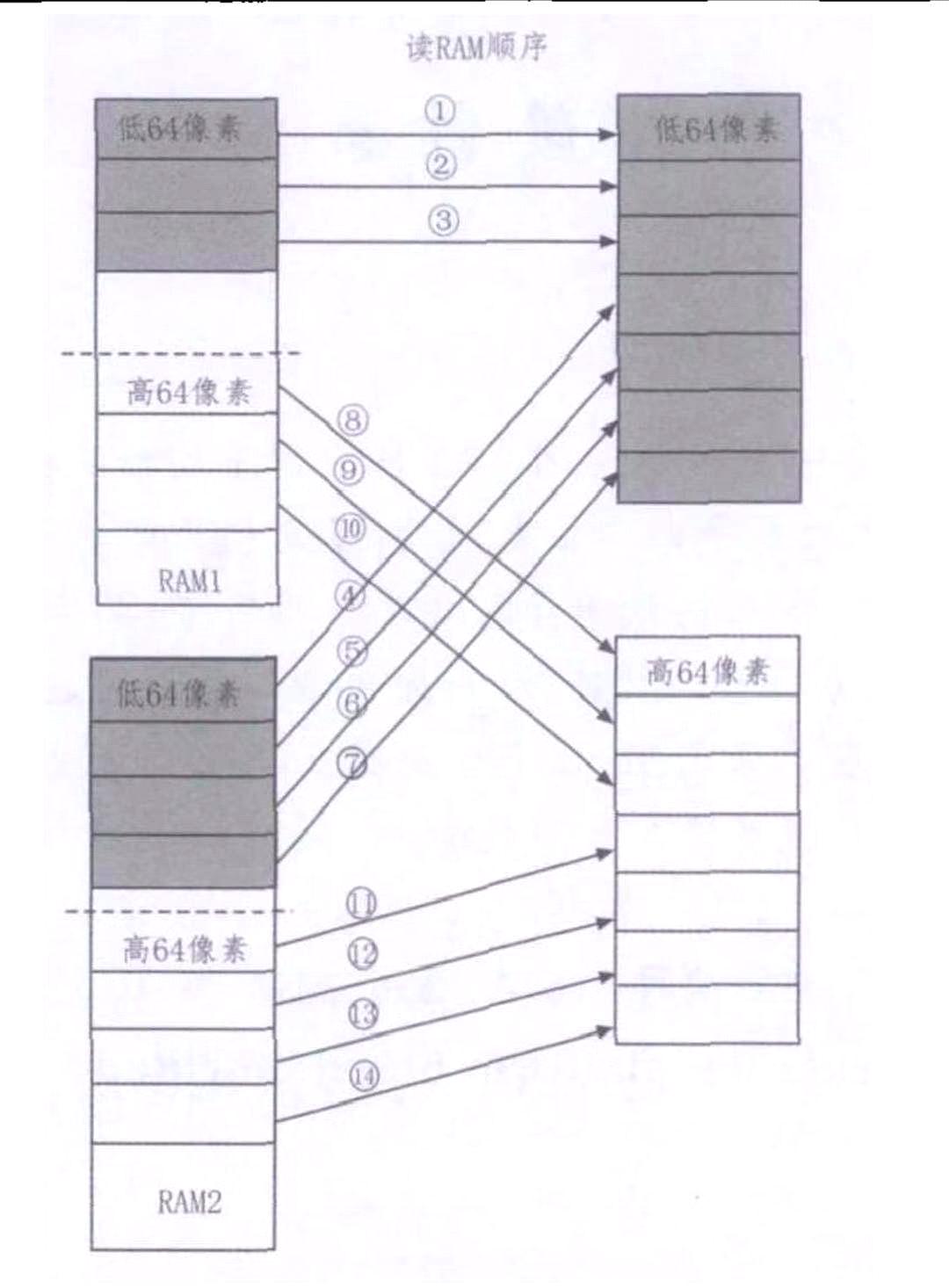

數據的讀取就是將每一次所采集的所有低能圖像數據和高能圖像數據依次傳輸到上位機圖像處理軟件中進行處理,所以本設計先讀取RAMI中的所有低能像素值,然後再讀取RAM2中的所有低能像素值,再然後讀取RAMI中的所有高能像素值,最後讀取RAM2中的所有高能像素值;這樣傳輸到上位機的圖像數據先是一幀低能的圖像數據然後是一幀高能的圖像數據,如圖4所示。

4仿真驗證

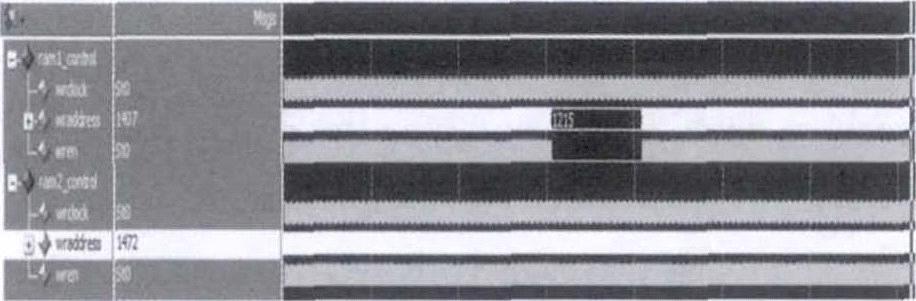

本設計模擬ADI前端雙能x射線探測器接3個探測板,AD2前端雙能探測器接4個探測板,所以仿真出來的信號如下圖所示。控製RAMI寫地址信號先從RAMI的地址0開始64個低能像素值,然後從地址1024開始寫64個高能像素值,經過3次反複之後,寫RAMI的最後一個地址會是1 2巧,之後會等待RAM2寫完本次數據之後再開始寫下一次數據,因為RAM2要緩存前端4個探測板采集的圖像數據,所以RAM2會比RAMI多出寫一個探測板采集的數據用的時間,當RAM2也將前端所采數據全部寫完後,RAMI和RAM2會同時開始寫人第二次采集的圖像數據,因為前文所述,寫RAM的地址會根據當前地址規律遞增,所以當第二次也寫完之後,RAMI的最後一個地址會是1407,如圖5所示。

圖5寫RAM仿真圖

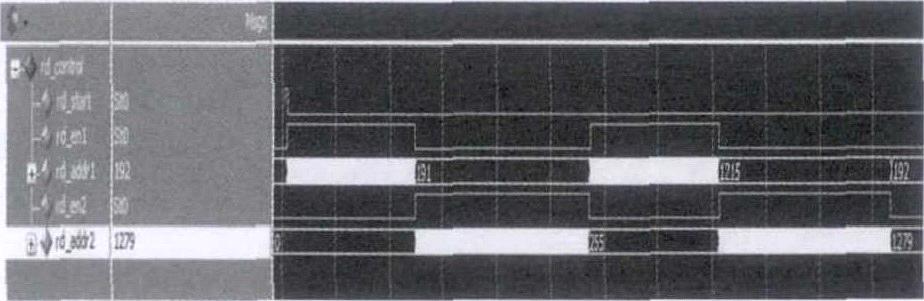

根據前文所述,讀取RAM數據時首先要先讀取 RAMI中所有低能像素值,由於ADI前端雙能x射線探測器接了3個探測板,所以緩存低能數據的地址為0到191,然後再讀取RAM2中所有低能像素值,而AD2前端雙能x射線探測器接了4個探測板,所以緩存低能數據的地址為0到255,再然後讀取 RAMI中所有的高能像素值,由於高能數據的緩存地址從1 024處開始,所以緩存高能數據的地址為 1 024到1 2巧,最後讀取RAM2中所有的高能像素值,緩存地址為1024到1279,如圖6所示。

圖6讀RAM仿真圖

當今社會集裝箱安檢機的應用越來越廣泛,為了更好地保證公共安全,同時又不降低生活效率,人們對集裝箱安檢機的要求也越來越高。武漢艾崴為了提高集裝箱安檢機數據采集傳輸速率,本文從圖像數據的排序人手,利用 FPGA的高速數據處理特性,並通過FPGA內部的存儲單元(M4K、M9K等)構造雙端口RAM,將前端采集到的圖像數據進行排列整齊以供上位機圖像處理軟件使用。用FPCA內部存儲器構造雙端口RAM不僅節省了大量邏輯,而且也為下級數據的讀取提供了友好的時序控製。因此利用FPGA對前端探測器采集的圖像數據進行排序不僅簡化了下級數據讀取控製邏輯而且提高了上位機圖像處理速度。